新闻中心

Xilinx Zynq-7000如何保护客户的知识产权

- 来源:Xilinx

- 发布时间:[2014-01-29]

摘要:本文描述了Xilinx Zynq-7000如何通过芯片内嵌的AES-256解密引擎和HMAC (Keyed-hashed message authentication code)认证引擎来保护客户的知识产权,防止拷贝、抄板等损害客户知识产权事件的发生。

基本原理:

Xilinx Zynq-7000内含AES-256解密引擎和HMAC认证引擎,并支持Secure Boot启动方式,用于保护客户的设计(包括软件的二进制可执行代码,数据以及FPGA的bitstream编程文件)不被窃取和使用。

客户在完成设计后,可以使用Xilinx ISE软件为设计添加用于认证的256-bit的校验码,然后再用256-bit密钥AES算法进行加密。

256-bit AES密钥由客户生成,保存在FPGA内部,不能被外部读取。

启动时,Zynq-7000首先执行芯片内部ROM中的代码。BOOTROM代码首先通过AES-256解密引擎对对被保护的设计进行解密,然后通过HMAC引擎认证完整性,只有通过认证的设计才能被加载并执行。

对于试图通过“抄板”窃取知识产权的行为,因为缺少和FLASH内容相对应的AES密钥,FLASH中内容将不会被加载并执行。256-bit AES密钥对应的组合达到1.15×1077种,可以充分保证客户知识产权的安全。

Xilinx Zynq-7000内含的硬件安全引擎的特点:

1. HMAC硬件认证引擎

- 在内层保护客户设计不被非法篡改,保证客户设计的完整性。

- 使用美国国家标准技术研究所的SHA256 FIPS PUB-182-2算法和HMAC FIPS PUB-198 算法,这些算法由美国国家标准技术研究所(National Institute of Standards and Technology, NIST)提供

http://csrc.nist.gov/publications/fips/fips180-2/fips180-2withchangenotice.pdf

http://csrc.nist.gov/publications/fips/fips198-1/FIPS-198-1_final.pdf

- HMAC签名保存在Boot Image中。

2. AES-256硬件解密引擎

- 在外层保护客户设计不被反向工程,不被分析破解,不被拷贝。

- 密钥保存在片上的eFuse或者BBRAM(battery-backed RAM),不能被JTAG或者FPGA逻辑读取。eFuse仅支持一次可编程,掉电内容不丢失。BBRAM可支持反复编程,但是掉电内容丢失,因此需要外接电池。

- AES算法是美国国家标准技术研究所(National Institute of Standards and Technology, NIST)和美国商务部的正式标准(http://csrc.nist.gov/publications/fips/fips197/fips-197.pdf )。Xilinx支持最高安全等级的256-bit密钥加解密方式。

通过Xilinx ISE保护客户设计

Xilinx SDK用于生成Boot Image的工具支持SHA-256算法校验码生成和AES-256算法加密:

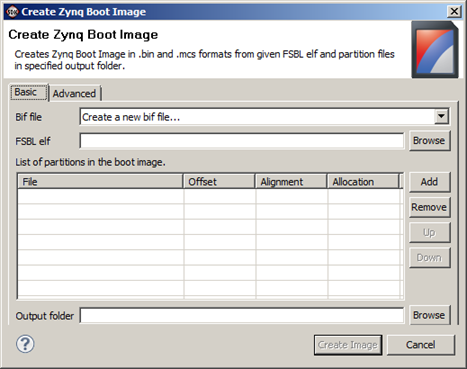

1. 启动Xilinx SDK

2. 点击Xilinx Tools->Create Boot Image,SDK弹出如下窗口

3. 在Tab Basic里面配置好输入的文件位置和生成的image的位置后,在Tab Advanced里面可以配置是否加密、密钥的存放位置以及密钥等内容:

在生成的Boot Image里面,偏移量0x28位置的内容决定了Boot Image是否加密:

Boot Image Header 0x028位置的内容 描述

0xA5C3C5A3 密钥保存在eFuse中

0x3A5C3C5A 密钥保存在BBRAM中

其他值 Boot Image未加密

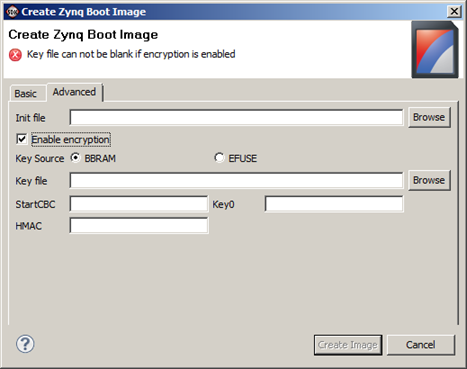

Boot Image的文件头和分区头不参与加密,被加密的只有各个分区的数据。Boot Image的格式如下图所示:

注意:

如果选择加密Boot Image,将对所有分区(Partition)的数据进行加密。

Zynq-7000的启动过程

Zynq-7000上电后首先执行芯片内部BootRom中的代码。BootRom中的代码由Xilinx开发并保证安全;代码保存在只读存储器中,用户无法修改。

BootRom支持三种启动模式:

- Secure, encrypted image, master mode

- Non-secure master mode

- Non-secure slave mode via JTAG

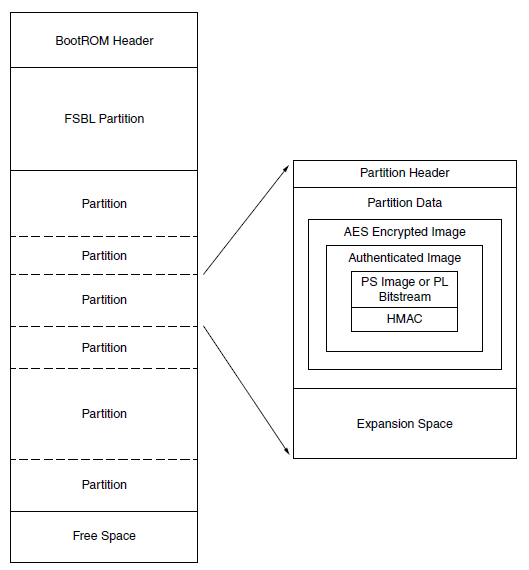

BootRom通过Boot Image文件头0x28位置的内容判断Boot Image是否加密,代码执行流程如下:

注意:

在Secure Boot Mode下,Boot Rom不会使能JTAG接口,这时无法通过JTAG读取Zynq-7000内部的信息,无论是软件二进制可执行代码,AES密钥,还是FPGA的配置信息。

Boot Image只有在认证了FSBL(First Stage Boot Loader)的完整性后,才会认为它是安全的,并将控制权移交给FSBL代码。 FSBL需要加载的Second Stage Boot Loader, 操作系统和应用可以是明文的,也可以是加密的。 一般不建议客户使用明文的PS (Processing System) Image。如果必须要这样做,需要充分考虑系统级别的安全性。如果这些内容是加密的,系统不允许切换AES密钥。

Secure Boot Mode仅限于NOR, NAND, SDIO, 和Quad-SPI flash,不支持JTAG或任何其他对外接口。

密钥的管理

256-bit AES密钥可以由用户指定,用Xilinx BitGen工具生成加密的bitstream,也可以由工具生成随机密钥。

AES密钥由Xilinx iMPACT软件通过JTAG写入Zynq-7000芯片中。

写入AES密钥时,所有FPGA中的存储器(密钥存储器和配置存储器)都会被清空。密钥写入后,没有任何办法可以重新读出写入的密钥,也不可能在不清空全部存储器的情况下改写密钥。

当采用BBRAM保存密钥时,需要在VCCBATT上外接电池,确保系统掉电的情况下BBRAM中的内容不会丢失。系统正常工作时,由VCCAUX对BBRAM供电,而不会使用VCCBATT上的电池供电。当系统掉电时,VCCBATT需要的电流很小(nA级别),一块手表纽扣电池可以使用很长时间。

其他Zynq-7000的安全要点

除了上面的内容,Xilinx还充分考虑了其他各种复杂情况下的如何保证用户知识产权的安全。

BootROM检测到Boot Image未加密后,进入非安全状态。AES解密引擎和HMAC认证引擎被关闭,只有上电复位才能使能它们。没有任何机制可以从非安全状态转换到安全状态(除了上电复位)。如果在加载未加密数据后试图加载加密数据,将导致系统锁定,只有重新上电后才能复位。

当PS或者PL检测到以下非法状态时,将清空OCM,系统缓存,复位PL,然后PS进入锁定状态。只有重新上电复位才能清楚系统锁定状态:

- Non-secure boot and eFuse secure boot set

- PS DAP enabled and JTAG chain disable eFuse set

- SEU error tracking has been enabled in the PS and the PL reports an SEU error

- A discrepancy in the redundant AES enable logic

- Software sets the FORCE_RST bit of the Device Configuration Control register

Xilinx Zynq-7000 BootRom支持fall-back功能:在当前的Boot Image不可用的情况下,会搜索并运行golden image。在这种情况下,系统要求golden image的加密状态和FSBL的加密状态是一致的,即:如果FSBL是加密的,golden image必须也是加密的;如果FSBL未加密,golden image必须也是不加密的。

在secure boot模式下,PS DAP和PL TAP控制器被关闭,这样排除了通过JTAG访问芯片内部的可能。

PS的DAP控制器可以通过eFuse的JTAG CHAIN DISABLE永久关闭。在生成PL bitstream时,可以配置DISABLE_JTAG选项(see UG628, Command Line Tools User Guide for more information),禁止通过JTAG访问PL。

小结

通过以上的分析,我们可以看到Xilinx Zynq-7000提供了充分的安全措施,来保证客户的知识产权和设计的安全性,是客户设计的重要选择。

参考文献:

UG585, Zynq-7000 EPP Technical Reference Manual

UG470, 7 Series FPGAs Configuration User Guide

最新活动

- 寻找《xilinx UltraScale™ MPSoC架构》 下载文档有奖

- 活动时间:2014/3/22-2014/5/22

- Xilinx Zynq交流群已开辟

- QQ群号:323470211,还有 Xilinx 资深工程师入驻,帮您答疑解惑!!!

- ZYNQ论坛互动专区

- ZedBoard及ZingBoard开发优秀手记展示,详情进入……