- 新闻中心

ADP5040: 集成1.2 A降压调节器和两个300 MA LDO的微型电源管理单元

- 发布人:ADI

- 发布时间:[2014-03-03]

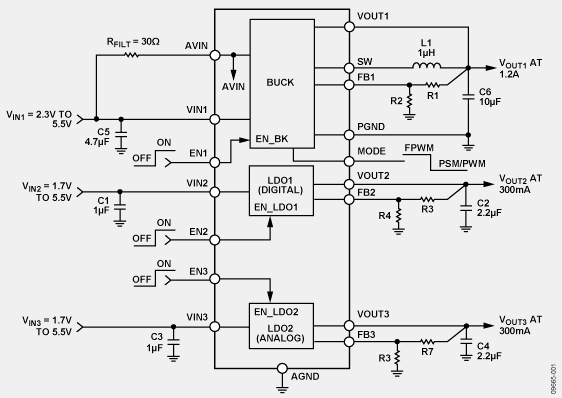

ADP5040在一个20引脚小型LFCSP封装中集成了一个高性能降压稳压器和两个低压差稳压器(LDO),可满足严苛的性能和电路板空间要求。

降压调节器的高开关频率支持使用小型多层外部器件,并使所需的电路板空间降至最小。

当MODE引脚设置为逻辑高电平时,降压调节器以强制脉冲宽度调制(PWM)模式工作。MODE引脚设为逻辑低电平时,如果负载在标称值左右,则降压调节器以PWM模式工作。当负载电流降至预定义阈值以下时,调节器以省电模式(PSM)工作,以便改善轻负载效率。ADP5040 LDO的低静态电流、低压差和宽输入电压范围可延长便携式设备的电池使用时间。在频率高达10 kHz时,ADP5040 LDO能保持60 dB以上的电源抑制性能,而所需的电压裕量则很低。

ADP5040中的各调节器通过对相应的使能引脚施加高电平来激活。调节器输出电压通过外部电阻分压器编程,可满足多种应用的需求。

特点和优势

输入电压范围:2.3 V至5.5 V

一个1.2 A降压调节器

两个300 mA LDO

20引脚4 mm x 4 mm LFCSP封装

过流和热保护

软启动

欠压闭锁

降压调节器主要特性

- 输出电压范围:0.8 V至3.8 V

- 电流模式拓扑结构,瞬态响应性能出色

- 工作频率:3 MHz

- 欲了解更多特性,请参考数据手册

LDO主要特性

- 输出电压范围:0.8 V至5.2 V

- 低VIN:1.7 V至5.5 V

- 利用2.2 μF陶瓷输出电容便可稳定工作

- 欲了解更多特性,请参考数据手册

ADP5040功能框图

精彩Webinar

- GSPS数据转换器与FPGA接口ADXL362

- 本在线研讨会讨论参考设计采用的转换技术以及可轻松连接FPGA的快速原型开发模块。

- 利用AD9361开发多路输入多路输出(MIMO)系统

- 研讨会详细介绍如何使用多个AD9361器件创建NxN MIMO系统,并探讨设计中需要权衡的一些问题。

- 使用ADAS1000系列模拟前端简化心电图(ECG)设计

- 研讨会将介绍ADAS1000系列低功耗心电图(ECG)模拟前端,以及如何使用ADAS1000系列产品。

- GSPS转换器宽带前端设计

- 研讨会讨论前端参数定义,然后概述有源与无源前端之间差异,随后在此基础上,将集中讨论无源前端。