新闻中心

将集成VCO和外部PLL电路的频率合成器杂散输出降至最低

- 来源:Analog_Devices

- 发布时间:[2013-04-03]

电路功能与优势

图1所示电路使用带集成式VCO和外部PLL的ADF4350频率合成器,通过隔离PLL频率合成器电路与VCO电路将杂散输出降至最低。

集成PLL和VCO的器件可从数字PLL电路馈通至VCO,由于PLL电路靠近VCO,会导致较高的杂散电平。

图1所示电路使用完全集成的小数N分频PLL和VCOADF4350,配合ADF4153PLL使用时,它可产生137.5MHz至4400MHz范围内的频率。

除了杂散性能改进外,使用外部PLL的另一潜在优势是可以增加频率分辨率。例如,如果选择ADF4157PLL取代ADF4153,PLL的频率分辨率可精细至0.7Hz。

图1. ADF4153PLL与ADF4350相连(原理示意图,所有连接和去耦均未显示)

电路描述

ADF4350是一款宽带PLL和VCO,由三个独立的多频段VCO组成。每个VCO涵盖约700 MHz的范围(VCO频率之间有部分重叠)。这样可提供2.2GHz至4.4GHz的基本VCO频 率范围。低于2.2 GHz的频率可使用DF4350的内部分频器生成。

对于大多数应用,ADF4350的内部PLL用于锁定VCO。除了锁定PLL,PLL电路的另一重要功能是VCO频段选择,即使用内部PLL的内部参考(R)和反馈(N)计数器比较VCO输出和参考输入。要完成频率生成,必须使能内部PLL,且必须设置所需频率。一旦频段选择已经耗去足够的时间,内部PLL可禁用,最后,可使能外部PLL。外部PLL比较参考频率与VCO输出频率以产生稳定的直流电压,用以锁定PLL。

图2显示了使用ADF4350内部PLL和VCO在RFOUTA+上测得的输出频率杂散,ADF4153 PLL禁用。请注意,13 MHz和26 MHz时存在PFD杂散。

图3显示了ADF4350内部PLL电路禁用、外部ADF4153 PLL有效时,在RFOUTA+上测得的输出杂散。在此模式下,ADF4153的电荷泵输出驱动环路滤波器,后者又驱动ADF4350的VTUNE 输入。VTUNE 输入控制ADF4350 VCO输出频率。

比较图2和图3可发现,在图2中由于鉴频鉴相器(PFD)频率(13 MHz和26 MHz时)产生的杂散在图3中消失在噪底中。

常见变化

可以选择不同的PLL。ADF4350和ADF4153内的小数N分频PLL具有PFD/4095的最低频率分辨率。如果需要更精细的分辨率,可以选择ADF4157。PLL的分辨率为PFD/225,从而提供<1 Hz的超精细分辨率。

对于需要更简单的软件编程能力的应用,ADF4150 PLL与ADF4350软件兼容,简化了软件编程序列。

图2. ADF4350在1.6GHZ时的PFD杂散

图3. 使用ADF4153 PLL时,ADF4350在1.6GHZ时的PFD杂散

电路评估与测试

ADF4153 PLL.CN-0232使用EVAL-ADF4350EB2Z板来评估所述电路,仅略作修改以加快设置和评估。EVAL-ADF4350EB2Z板使用标准ADF4350编程软件,该软件包含在评估板附带的光盘上。EVAL-ADF4153EBZ1评估板自带用于ADF4153 PLL的软件。

设备要求

- 带编程软件的EVAL-ADF4350EB2Z。

- 带编程软件的EVAL-ADF4153EBZ1。

- 5.5 V电源。

- R&SSMA100A信号发生器或等效器件。

- R&SFSUP26频谱分析仪或等效器件。

两台运行Windows® XP、Windows Vista(32位)或Windows7(32位)的PC,一台带USB端口,另一台带打印机端口。如果两种端口都没有,可使用EVAL-ADF4xxxX-USBUSB适配器套件代替打印机端口。

需要SMA同轴电缆将EVAL-ADF4350EB2Z的RFOUTB+连接至EVAL-ADF4153EBZ1的RFIN。另外需要简单的SMA分路器,以便在两个电路板之间共享基准电压源。需要某种柔 性微型同轴电缆将ADF4153环路滤波器的输出连接到ADF4350 VTUNE输入。为了将无用干扰降至最低,电缆两端必须接地至各电路板上的适当GND点。

功能框图

本实验中使用EVAL-ADF4153EBZ1 和EVAL-ADF4350EB2Z。选择EVAL-ADF4350EB2Z是因为它含有辅助RFOUTB+输出级,该级通过SMA电缆连接到EVAL-ADF4153EBZ1,如图4所示。

两个PLL使用相同的基准输入(REFIN)频率;因此SMA分路器将相同REFIN连接到两个电路板。

EVAL-ADF4153EBZ1上的环路滤波器输出通过屏蔽同轴电 缆连接到ADF4350的VTUNE引脚,以确保引脚上无额外噪声 或杂散。两个器件是单独编程的。可能需要为每个电路板使用不同PC,以确保硬件驱动器之间不发生冲突。

开始使用

UG-110用户指南详细说明了的安装和使用。UG-110还包理图、布局和物料清单。

UG-167用户指南包含关于EVAL-ADF4153EBZ1的类似信息。电路板上必要的修改是去除了VCO (Y1)。为了将该电路板重新配置为输入,去除了R7电阻,并将R8和R9改变为0。

ADF4350板上的PLL环路滤波器未被时,微型同轴电缆可用于将ADF4153出连接到ADF4350 (T4)的VTUNE引脚。须连接到两个电路板上的接地点。

图4. 测试设置功能框图

初始化程序

ADF4350必须为每个新频率执行频段选择。

1.正常初始化ADF4350(设置R5、R4、R3、R2、R1、R0),但DB4、R2设置为1(ICP三态使能),因为ADF4350电荷泵未被使用。将DB9、R4设置为0,以实现RFOUTB+上的分频VCO输出。使能RFOUTB+(辅助输出)。此信号经同轴电缆馈入ADF4153。

2.初始化ADF4153(根据数据手册),以接受VCO输出频率作为RF输入频率。请注意,频段选择开关位于内部;因此不需要外部开关来去除PLL VTUNE。

3.ADF4153实现锁定时,必须将ADF4350计数器复位到1 (DB3、R2)。不激活计数器复位会降低杂散性能。此外,所有ADF4350频率合成器模块可使用测试模式位 (DB10、R5)关断。

图5. ADF4350软件窗口

频率更新

1.将DB10、R5设置为0以重新激活ADF4350频率合成器模块。

2.将ADF4350的DB3、R2设置为0以取消计数器复位,因为频段选择需要这些计数器。

3. 根据需要为新频率设置ADF4350和ADF4153 N计数器寄存器。

4.ADF4153实现锁定时,可激活ADF4350计数器复位(DB3、R2)。此外,所有频率合成器模块可使用测试模式位(DB10、R5)关断。

5.视需要为新频率重复第1至第4步。

图5和图6中显示的软件屏幕截图显示了26MHzIN (ADF4350) 和13 MHz PFD (ADF4153)的软件窗口。

设置设备后,使用标准RF测试方法测量输出信号的频谱纯度。

图6. ADF4153软件窗口

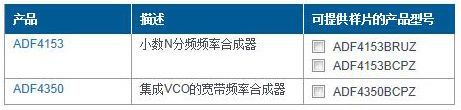

此电路中的所有产品:

最新活动

- ADI 在线设计峰会 2013

- 会议时间:2013年9月25日--2013年12月5日

- ADI最新技术资料,评帖子有奖

- 活动时间:2013年2月27日--2013年12月31日

- 晒样片,拿礼品!

- 活动时间:2013年2月27日--2013年12月31日